設置MX8MP LVDS clock

Calculate PLL_1443X_RATE()

Fout=((m + k/65536) × Fin) / (p × 2^s)

Fin is 24 MHz and Fout is LVDS clock MHz x 7, then calculate m,

| Fout | m | S | p | k | LVDS clock | LVDS Resolution |

|---|---|---|---|---|---|---|

| 280000000 | 93 | 2 | 2 | 0 | 40000000 | 800x600 |

| 231000000 | 77 | 2 | 2 | 0 | 33000000 | |

| 189000000 | 63 | 2 | 2 | 0 | 27000000 | |

| 174750000 | 58 | 2 | 2 | 0 | 24964286 | |

| 171000000 | 57 | 2 | 2 | 0 | 24428571 | |

| 210000000 | 70 | 2 | 2 | 0 | 30000000 | |

| 453000000 | 151 | 2 | 2 | 0 | 64700000 | 1024x768 |

| 357000000 | 119 | 2 | 2 | 0 | 51000000 | 1024x600 |

Contents

- 1Comment out LVDS clock fix at 74.25MHz,

- 2Add Fout clock into imx8mp.dtsi. Example to set LVDS clock to 30MHz.

- 3Add PLL_1443X_RATE to driver.

- 4Add LVDS timing clock into panel-simple.c.

- 5Rebuild kernel image and dtb file.

- 6Check the LVDS output clock:

Comment out LVDS clock fix at 74.25MHz,

diff --git a/drivers/gpu/drm/imx/imx8mp-ldb.c b/drivers/gpu/drm/imx/imx8mp-ldb.c index be969f453587..f1672f392122 100644 --- a/drivers/gpu/drm/imx/imx8mp-ldb.c +++ b/drivers/gpu/drm/imx/imx8mp-ldb.c @@ -198,11 +198,12 @@ imx8mp_ldb_encoder_atomic_check(struct drm_encoder *encoder, * Due to limited video PLL frequency points on i.MX8mp, * we do mode fixup here in case any mode is unsupported. / + / if (ldb->dual) mode->clock = mode->clock > 100000 ? 148500 : 74250; else mode->clock = 74250; - + */ return 0; } @@ -224,12 +225,13 @@ imx8mp_ldb_encoder_mode_valid(struct drm_encoder *encoder, * Due to limited video PLL frequency points on i.MX8mp, * we do mode valid check here. / + / if (ldb->dual && mode->clock != 74250 && mode->clock != 148500) return MODE_NOCLOCK; if (!ldb->dual && mode->clock != 74250) return MODE_NOCLOCK; - + */ return MODE_OK; }

Add Fout clock into imx8mp.dtsi. Example to set LVDS clock to 30MHz.

</li> </ol>

Fout is 30MHzx7=210000000.

diff --git a/arch/arm64/boot/dts/freescale/imx8mp.dtsi b/arch/arm64/boot/dts/freescale/imx8mp.dtsi index 7e71a112c618..408ced2aa378 100644 --- a/arch/arm64/boot/dts/freescale/imx8mp.dtsi +++ b/arch/arm64/boot/dts/freescale/imx8mp.dtsi @@ -823,7 +823,8 @@ clk: clock-controller@30380000 { <800000000>, <393216000>, <361267200>, - <1039500000>; + //<1039500000>; + <210000000>; };

Add PLL_1443X_RATE to driver.

Yocto 3.0 path: imx8mp_videopll_tbl[] at drivers/clk/imx/clk-imx8mp.c

Yocto4.0 path: imx_p111443_tb1[] at drivers/clk/imx/clk-pll14xx.c

diff --git a/drivers/clk/imx/clk-pll14xx.c b/drivers/clk/imx/clk-pll14xx.c

index 1563a7bff422..0882aeb196bb 100644

--- a/drivers/clk/imx/clk-pll14xx.c

+++ b/drivers/clk/imx/clk-pll14xx.c

@@ -62,6 +62,7 @@ static const struct imx_pll14xx_rate_table imx_pll1443x_tbl[] = {

PLL_1443X_RATE(519750000U, 173, 2, 2, 16384),

PLL_1443X_RATE(393216000U, 262, 2, 3, 9437),

PLL_1443X_RATE(361267200U, 361, 3, 3, 17511),

+ PLL_1443X_RATE(210000000U, 70, 2, 2, 0),

};

struct imx_pll14xx_clk imx_1443x_pll = {

Add LVDS timing clock into panel-simple.c.

Example modify for g070vvn01.

diff --git a/drivers/gpu/drm/panel/panel-simple.c b/drivers/gpu/drm/panel/panel-simple.c

index 22840352fdcf..ce13868206ee 100644

--- a/drivers/gpu/drm/panel/panel-simple.c

+++ b/drivers/gpu/drm/panel/panel-simple.c

@@ -1363,15 +1363,15 @@ static const struct panel_desc auo_b140han06 = {

};

static const struct display_timing auo_g070vvn01_timings = {

- .pixelclock = { 33300000, 34209000, 45000000 },

+ .pixelclock = { 30000000, 30000000, 30000000 },

.hactive = { 800, 800, 800 },

- .hfront_porch = { 20, 40, 200 },

- .hback_porch = { 87, 40, 1 },

- .hsync_len = { 1, 48, 87 },

+ .hfront_porch = { 20, 20, 20 },

+ .hback_porch = { 100, 100, 100 },

+ .hsync_len = { 64, 64, 64 },

.vactive = { 480, 480, 480 },

- .vfront_porch = { 5, 13, 200 },

- .vback_porch = { 31, 31, 29 },

- .vsync_len = { 1, 1, 3 },

+ .vfront_porch = { 3, 3, 3 },

+ .vback_porch = { 2, 2, 2 },

+ .vsync_len = { 4, 4, 4 },

};

static const struct panel_desc auo_g070vvn01 = {

@@ -1379,8 +1379,8 @@ static const struct panel_desc auo_g070vvn01 = {

.num_timings = 1,

.bpc = 8,

.size = {

- .width = 152,

- .height = 91,

+ .width = 261,

+ .height = 163,

},

.delay = {

.prepare = 200,

Rebuild kernel image and dtb file.

Load imx8mp-rom5722-a1-lvds0-auo.dtb file for checking the result.

// SPDX-License-Identifier: (GPL-2.0+ OR MIT)

/*

- Copyright 2019 NXP

*/

- include "imx8mp-rom5722-a1.dts"

/ {

lvds_panel: lvds_panel {

compatible = "auo,g070vvn01";

backlight = <&lvds_backlight0>;

port {

panel_lvds_in: endpoint {

remote-endpoint = <&lvds_out>;

};

};

};

};

&ldb {

status = "okay";

lvds-channel@0 {

fsl,data-mapping = "spwg";

fsl,data-width = <24>;

status = "okay";

port@1 {

reg = <1>;

lvds_out: endpoint {

remote-endpoint = <&panel_lvds_in>;

};

};

};

};

&ldb_phy {

status = "okay";

};

&lvds_backlight0 {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_lvds_vcc_0 &pinctrl_bklt_vcc_0>;

lvds-vcc-enable = <&gpio1 6 GPIO_ACTIVE_LOW>; /* LCD0_VDD_EN */

lvds-bkl-enable = <&gpio1 0 GPIO_ACTIVE_LOW>; /* LCD0_BKLT_EN */

status = "okay";

};

~

~

~

~

~

~

~

~

~

~

~

"arch/arm64/boot/dts/freescale/imx8mp-rom5722-a1-lvds0-auo.dts" 48L, 813C

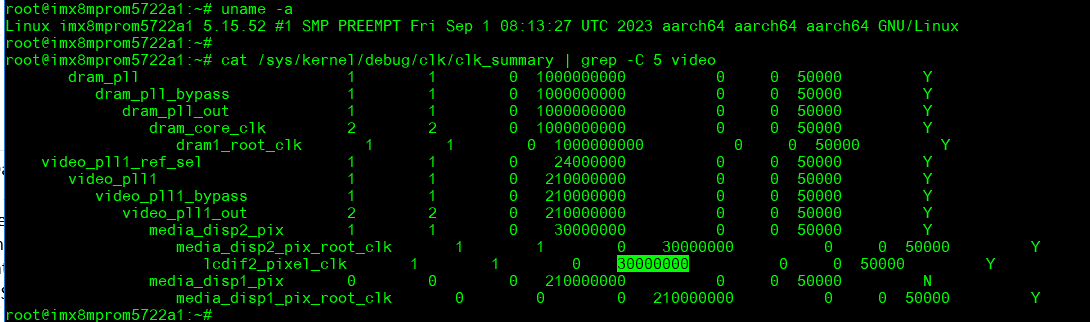

Check the LVDS output clock:

cat /sys/kernel/debug/clk/clk_summary | grep -C 5 video